Наверх

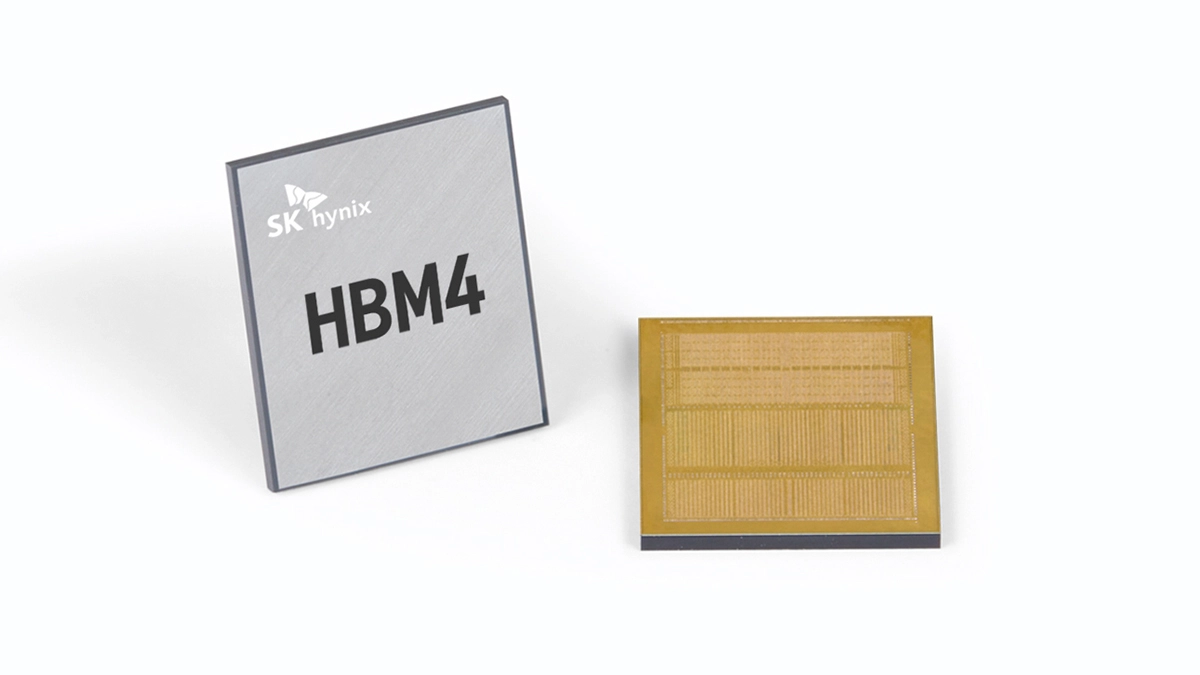

НаверхПамять будущего SK Hynix представляет HBM4 с 2048-битным интерфейсом

Скорость 10 ГТ/с и революционная архитектура — как HBM4 от SK Hynix изменит игры и высокопроизводительные вычисления.

SK Hynix завершила разработку своей памяти HBM4 и подготовила ее к массовому производству стеков памяти, сообщила компания в пятницу. Стеки HBM4 от SK Hynix превосходят спецификации, установленные JEDEC, на 25% по производительности, хотя пока неизвестно, смогут ли производители ИИ-ускорителей следующего поколения — такие как AMD, Broadcom или Nvidia — использовать этот потенциал в своих продуктах 2026 года.

Стеки памяти HBM4 от SK Hynix оснащены 2048-битным вводом-выводом, что удваивает ширину интерфейса HBM впервые с 2015 года, и скоростью передачи данных 10 ГТ/с, что на 25% выше официального стандарта JEDEC (подробнее об этом позже). В стеках памяти HBM4 компании используются специально разработанные кристаллы DRAM, изготовленные по проверенной технологии 1b-нм (5-е поколение 10-нм класса), которая сочетает достойную энергоэффективность с зрелостью узла (т. е. низкой плотностью дефектов и вариативностью).

Для своих модулей HBM4 SK Hynix продолжает использовать свой проверенный метод Advanced Mass Reflow Molded Underfill (MR-MUF). В этом процессе несколько чипов памяти размещаются на базовой подложке и соединяются вместе за один этап оплавления. Сразу после этого пространства между сложенными слоями DRAM, базовым кристаллом и подложкой заполняются формовочным материалом для закрепления и защиты структуры. Усовершенствованный MR-MUF позволяет компании поддерживать высоту своих 12-слойных стеков HBM в пределах спецификации и улучшать теплоотвод энергоемких модулей памяти.

«Завершение разработки HBM4 станет новой вехой для отрасли», — сказал Джухван Чо, глава отдела разработки HBM в SK Hynix, который руководил разработкой. «Поставляя продукт, отвечающий потребностям клиентов в производительности, энергоэффективности и надежности своевременным образом, компания обеспечит выход на рынок в срок и сохранит конкурентные позиции».

К сожалению, SK Hynix не раскрывает ни количество слоев DRAM, используемых в ее устройствах HBM4, ни их емкость, хотя, скорее всего, речь идет о 12-слойных устройствах емкостью 36 ГБ, которые будут использоваться в графических процессорах для дата-центров Nvidia Rubin, но это лишь предположения. Компания также не сообщает, используют ли ее первоначальные стеки HBM4 базовые логические кристаллы 12FFC+ (12-нм класс) или N5 (5-нм класс), произведенные TSMC.

Пожалуй, самая интересная часть анонса SK Hynix заключается в том, что компания решила выйти за рамки спецификации JEDEC и сертифицировать свои стеки HBM4 на скорость передачи данных 10 ГТ/с, в то время как стандарт устанавливает 8 ГТ/с. Компания не одинока в своем стремлении превзойти спецификации JEDEC для HBM4: Micron в настоящее время поставляет образцы устройств HBM4 со скоростью передачи данных 9,2 ГТ/с, в то время как у Rambus есть контроллер памяти HBM4, способный работать на скорости 10 ГТ/с. Хотя дополнительная производительность может быть использована разработчиками чипов в какой-то момент, большинство из них, по-видимому, хотят иметь некоторый запас для дополнительной уверенности, согласно инсайту, которым Rambus поделилась несколько лет назад.

SK Hynix заявляет, что готова к массовому производству своих стеков HBM4, хотя не сообщает, когда планирует начать серийное производство HBM4.

«Мы объявляем о создании первой в мире системы массового производства HBM4», — сказал Джастин Ким, президент и глава подразделения AI Infra в SK Hynix. «HBM4, символический поворотный пункт за пределами ограничений инфраструктуры ИИ, станет ключевым продуктом для преодоления технологических вызовов. Мы превратимся в поставщика полного стека памяти для ИИ, своевременно поставляя продукты памяти наилучшего качества и разнообразной производительности, требуемые в эпоху ИИ».

Слухи о видеокартах Nvidia RTX 50 SUPER: все, что известно на данный момент